La réduction de la feuille de route de TSMC pour le silicium pourrait signifier de grandes choses pour vos appareils Apple

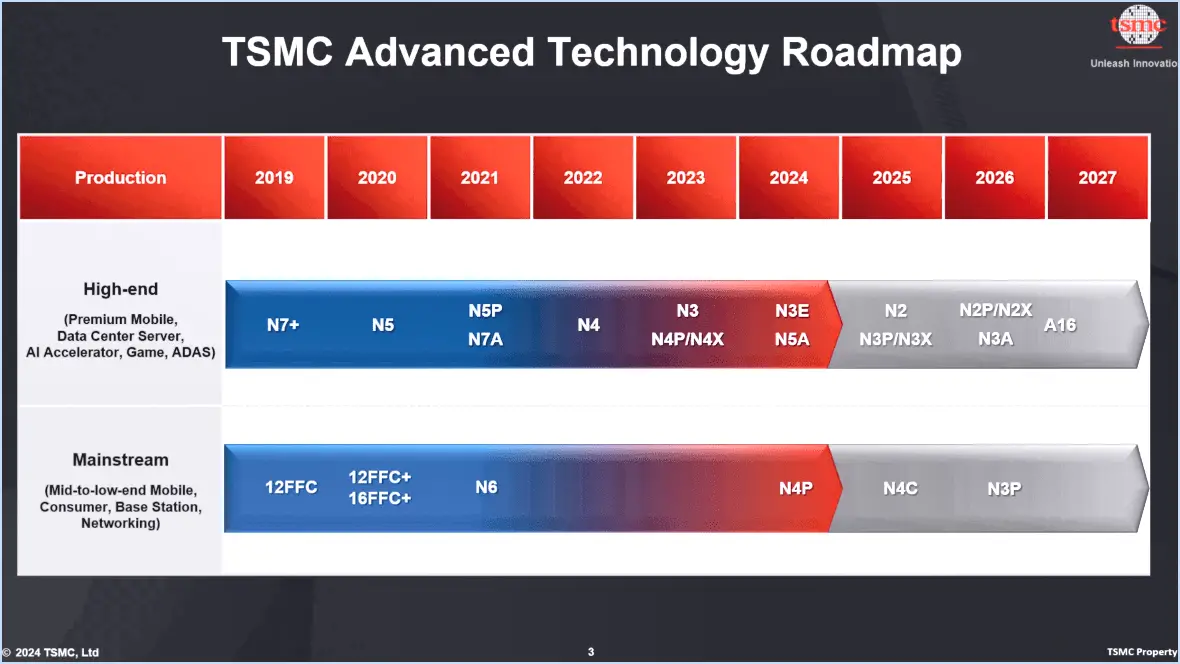

La société Taiwan Semiconductor Manufacturing Company (TSMC) vient de tenir son symposium technologique 2024 en Amérique du Nord, au cours duquel elle a informé les participants et les investisseurs de sa feuille de route technologique pour l'avenir.

Vous pouvez vous demander à juste titre : d'accord, mais qu'est-ce que cela a à voir avec moi, utilisateur de produits Apple ? TSMC est une entreprise de fabrication de puces, probablement la plus avancée au monde. Elle est le partenaire d'Apple pour la quasi-totalité de ses principales puces - la série A pour les iPhones et les iPads, la série M pour les Macs, etc. Apple est souvent le premier à bénéficier des nouveaux processus de fabrication de TSMC, payant une prime pour être le premier client à utiliser les technologies 5nm ou 3nm, par exemple.

Voici un résumé de la feuille de route de TSMC et de ce qu'elle pourrait signifier pour le futur silicium d'Apple, et donc pour les futurs iPhones, iPads, Macs et autres.

Qu'est-ce qu'un nanomètre ?

Avant de parler des technologies futures de TSMC, rappelons rapidement ce qu'est un "nanomètre" dans ce contexte. Techniquement, c'est un milliardième d'un mètre. Un cheveu humain a une épaisseur comprise entre 50 000 et 100 000 nm. La plupart des bactéries ont une épaisseur comprise entre 1 000 et 10 000 nanomètres.

Dans la technologie des procédés au silicium, la mesure du "nanomètre" correspond à la taille de certaines caractéristiques de la puce. Différentes entreprises mesurent différentes caractéristiques - il s'agissait autrefois de la longueur entre la source et le drain d'un transistor à effet de champ (FET), mais de nos jours, différentes parties sont mesurées par différentes entreprises.

La puce A17 Pro a été le premier processeur 3nm d'Apple, suivi par le M3.

La puce A17 Pro a été le premier processeur 3nm d'Apple, suivi par le M3.

La puce A17 Pro a été le premier processeur 3nm d'Apple, suivi par le M3.

En d'autres termes, 5 nm signifie que certaines parties spécifiques de la puce ne mesurent que 5 nanomètres, mais le 5 nm de TSMC n'est pas le même que le 5 nm d'Intel, ni le 5 nm de Samsung, etc. Un nombre de nanomètres plus petit signifie que vous pouvez insérer plus de logique ou de cache ou autre dans le même espace, ce qui peut conduire à des puces plus puissantes, à une consommation d'énergie plus faible, à des puces plus petites qui s'intègrent dans des appareils plus petits, etc.

C'est un peu comme regarder une ville dans Apple Maps : un zoom arrière rend tout plus petit, en mettant plus de bâtiments, de rues et de terrains sur la même surface d'écran. C'est ce que signifie le passage à un processus nanométrique plus petit : plus de "ville" dans le même espace.

Il existe de nombreux autres aspects importants d'un microprocesseur, notamment la manière dont les transistors sont isolés, les matériaux utilisés et bien d'autres choses encore, mais la mesure du "nanomètre" est restée comme un moyen de différencier une grande génération de fabrication d'une autre.

Progrès à 3 nm

Apple a été le premier à utiliser le processus 3nm initial de TSMC, appelé N3. L'entreprise l'a maintenant affiné avec le processus N3E, que nous pensons qu'Apple utilisera dans ses produits les plus avancés cet automne (A18 et M4). Bien que cela puisse sembler important, l'objectif principal du N3E est de rendre les puces plus abordables. Il existe de légères différences en termes de densité et de performances, mais il ne s'agit pas d'un changement de génération majeur.

2nm l'année prochaine

Le prochain changement majeur est le passage au 2nm, qui devrait avoir lieu en 2025. Apple devrait à nouveau être le premier client important (et peut-être le seul), il est donc possible que l'A19 ou d'autres puces (peut-être un M5 ?) qui seront livrées fin 2025 utilisent ce processus. Tout dépend de la capacité de TSMC à résoudre les problèmes de fabrication, de rendement et autres à temps pour produire des dizaines de millions de puces avec ce procédé.

Par rapport au procédé N3E, le procédé N2 devrait permettre de réduire la consommation d'énergie de 25 à 30 % (pour une puce de même complexité et de même fréquence) ou d'améliorer les performances de 10 à 15 % à consommation d'énergie égale. La densité des puces (la quantité d'éléments qui tiennent dans une seule zone) devrait augmenter de 15 %.

Un changement intéressant pour cette génération de puces, en plus d'être simplement plus petites/denses/rapides, est quelque chose que TSMC appelle "NanoFlex". Il permettra aux concepteurs de puces d'utiliser des cellules provenant de différentes bibliothèques de puces sur la même plaquette. Habituellement, un concepteur de puce doit utiliser tous les blocs d'une bibliothèque "faible consommation", "haute densité" ou "haute performance", en fonction des besoins les plus importants de la puce. En permettant aux concepteurs d'utiliser différentes parties de différentes bibliothèques, les puces peuvent adapter les différents domaines à leurs besoins.

Par exemple, Apple pourrait décider qu'il est plus important de rendre les encodeurs et décodeurs vidéo et audio de la puce aussi petits que possible et de concevoir cette partie de la puce en utilisant les bibliothèques de conception à haute densité tout en utilisant les bibliothèques à faible consommation d'énergie pour les cœurs de CPU à faible consommation et les bibliothèques à haute performance pour les cœurs de CPU à haute performance.

Pour les puces produites par Apple, le facteur limitant tend à être la puissance et la dissipation thermique. On peut donc s'attendre à ce que les puces fabriquées avec le procédé N2 contiennent plus de « choses » (cœurs, cache, encodeurs vidéo plus grands et plus complexes, etc.), à hauteur de 15 à 20 %, avec des vitesses d'horloge et donc des performances légèrement plus élevées, par rapport aux puces de l'année précédente. Toutefois, la capacité d'optimiser des parties spécifiques de la puce à l'aide d'outils provenant de différentes bibliothèques de puces peut s'avérer très rentable en termes de performances « maximales » plus élevées ou de consommation d'énergie en mode veille plus faible.

L'année suivant la sortie du N2, TSMC proposera deux versions améliorées du processus : N2P, axée sur les performances maximales, et N2X, axée sur les tensions et la consommation d'énergie réduites. On ne sait pas si Apple adoptera l'une de ces versions pour les puces qui arriveront en 2026.

A16 - On fait des angströms maintenant ?

Le principal changement après le 2 nm (N2) est un processus que TSMC appelle A16 (aucun rapport avec l'A16 Bionic). Il s'agit d'un processus de 1,6 nanomètre, mais maintenant que les choses deviennent si petites, ils abandonnent en quelque sorte les « nanomètres » pour passer aux « angströms ». Un angstrom est un dix-milliardième de mètre, soit 10 fois plus petit qu'un nanomètre.

Celle-ci n'arrivera pas avant la fin de l'année 2026, presque certainement trop tard pour qu'Apple puisse l'utiliser cette année-là. Les puces fabriquées avec le procédé A16 d'Apple apparaîtront très probablement en 2027.

TSMC a donné quelques premières estimations par rapport au processus N2P à venir, où A16 devrait améliorer les performances de 8 à 10 pour cent à la même tension et complexité ou réduire la puissance de 15 à 20 pour cent à la même fréquence et au même nombre de transistors.

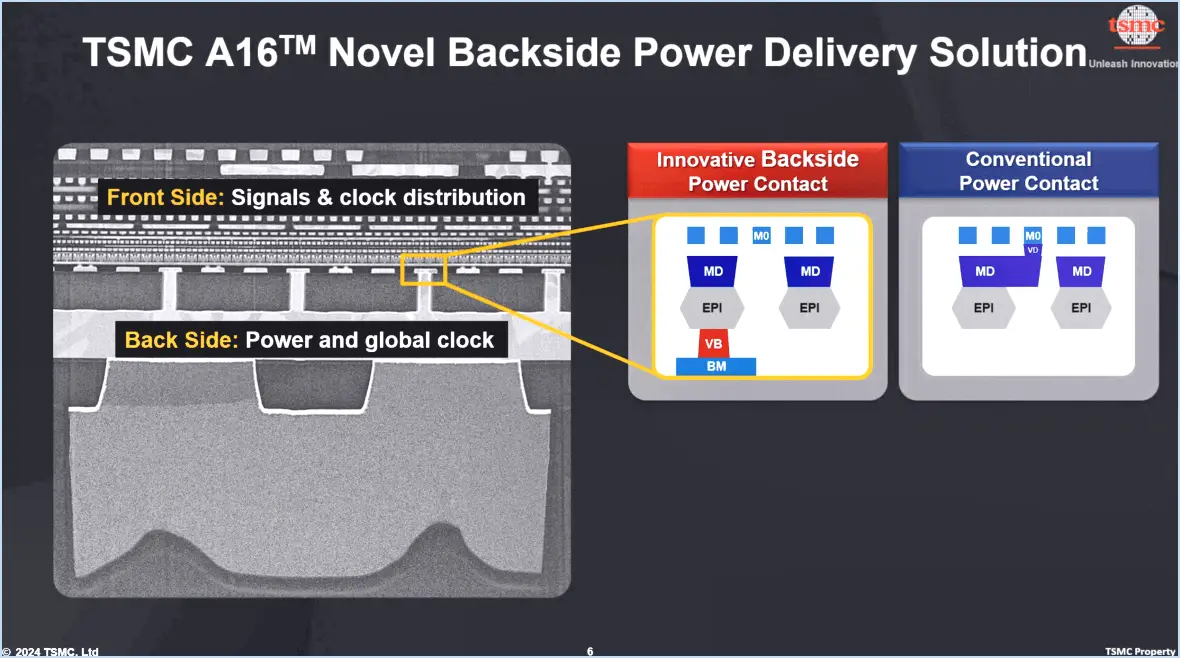

La grande innovation de la génération A16 sera la fourniture d'énergie à l'arrière, ce que TSMC appelle "Super Power Rail". Il s'agit d'un réseau de distribution d'énergie sur la face arrière de la plaquette de silicium, relié aux transistors par de petits tunnels. Cela améliore la densité et potentiellement la fiabilité, car l'alimentation ne doit pas être acheminée avec toutes les lignes de distribution de signaux et d'horloges sur la face supérieure de la puce. D'autres fabricants de puces poursuivent des technologies similaires (on pense notamment à PowerVia d'Intel) - des approches fondamentalement différentes pour une même idée.

TSMC pourrait être un peu plus en retard que des concurrents comme Intel avec ce type de technologie, car elle a été légèrement repoussée. Elle devait à l'origine être introduite dans le processus N2P, mais elle le sera désormais dans le processus A16.

Les puces dans les produits Apple qui utilisent le processus A16 seront capables d'avoir encore plus de choses (plus de cœurs, plus de caches) que le processus N2 tout en conservant le même profil de puissance.

L'un des grands avantages d'Apple est de disposer plus tôt que les autres de puces plus denses ou présentant un meilleur profil énergétique, mais la véritable magie vient de l'excellence de la conception des puces et du développement de logiciels qui optimisent les logiciels d'Apple spécifiquement pour les puces qu'ils produisent.